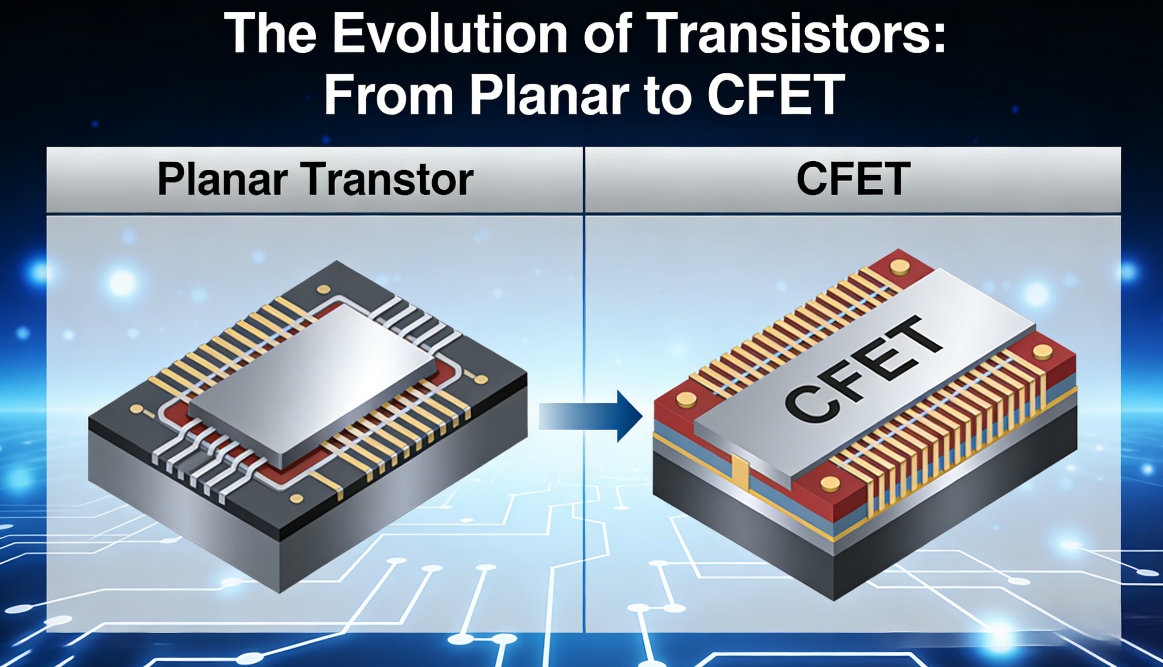

تکامل ترانزیستور: از مسطح تا CFET، ادغام سه بعدی پیشرفت نیمه هادی را دوباره تعریف می کند

برای بیش از نیم قرن، صنعت نیمه هادی با پیروی از یک قانون ساده رشد کرد: کوچکتر کردن ترانزیستورها.کوچک شدن اندازه ویژگی عملکرد بالاتر، توان کمتر و هزینه کمتر برای هر ترانزیستور را ارائه می دهد.اما امروزه این مسیر به مرز فیزیکی و اقتصادی خود رسیده است.دوران مقیاس بندی خالص به پایان رسیده است و دوره جدیدی از نوآوری ساختاری و ادغام سه بعدی آغاز شده است.

خود ترانزیستور در حال دستخوش یک انقلاب کامل معماری است.از MOSFET مسطح تا FinFET، از نانوصفحه GAA تا انباشته CFET، هر مرحله نشان دهنده یک تغییر از کوچک شدن به بازسازی ترانزیستور در سه بعدی.این فقط بهبود تدریجی نیست، بلکه یک تعریف مجدد کامل از نحوه ارائه عملکرد تراشه ها است.

چهار نسل از معماری ترانزیستور

1. ترانزیستور مسطح (دو بعدی سنتی)

ساختار تخت کلاسیک، جایی که دروازه کانال را از بالا کنترل می کند.از روزهای اولیه تا 40 نانومتر و 28 نانومتر تسلط داشت.با کاهش بیشتر ابعاد، جریان نشتی و کنترل الکترواستاتیکی به مشکلاتی غیرقابل حل تبدیل شدند.

2. FinFET (کنترل گیت سه بعدی)

کانال به یک "باله" عمودی تبدیل می شود که دروازه در اطراف سه طرف پیچیده می شود.این به شدت کنترل الکترواستاتیک را بهبود میبخشد، نشت را کاهش میدهد و مقیاسپذیری را تا 7 نانومتر، 5 نانومتر و حتی 3 نانومتر امکانپذیر میکند.FinFET پایه و اساس عصر تراشه های مدرن با کارایی بالا شد.

3. نانوصفحه GAA (Gate-All-Around)

در 2 نانومتر و پایین تر، FinFET به حد خود می رسد.GAA باله را با نانوسیمها یا ورقهای افقی روی هم جایگزین میکند که کاملاً توسط دروازه احاطه شده است.کنترل بهتر، قدرت کمتر و جریان درایو بالاتر را ارائه می دهد.GAA اکنون ساختار اصلی تراشههای کلاس 2 نانومتری در سراسر TSMC، سامسونگ و اینتل است.

4. CFET (FET مکمل)

مرز بعدی: چیدن NMOS و PMOS به صورت عمودی.CFET دو ترانزیستور را در ردپای یک ترانزیستور بسته بندی می کند که به شدت سطح را کاهش می دهد و تراکم را بهبود می بخشد.این پایان تکاملی نهایی مقیاس ترانزیستور است قبل از اینکه یکپارچه سازی سیستم سه بعدی واقعی به دست بیاید.

چرا پوسته پوسته شدن به تنهایی دیگر کار نمی کند؟

- هزینه های فرآیند در هر گره جدید به طور تصاعدی افزایش می یابد

- نشت کوانتومی و محدودیت های فیزیکی محدودیت ها را سخت می کند

- تأخیر اتصال و مصرف برق از سرعت ترانزیستور پیشی می گیرد

- تراشه های یکپارچه بزرگ از بازده کم و هزینه بالا رنج می برند

صنعت متوجه شده است: عملکرد دیگر از ترانزیستورهای کوچکتر حاصل نمی شود.از آن می آید اتصالات بهتر، معماری هوشمندتر و ادغام عمودی.

عصر جدید: سه لایه نوآوری سه بعدی

پیشرفت نیمه هادی اکنون با سه بعد طراحی سه بعدی تعریف می شود:

- ترانزیستور سه بعدی: FinFET، GAA، CFET – ساخت ترانزیستور به صورت عمودی

- انباشتن دستگاه سه بعدی: حافظه روی منطق، پیوند هیبریدی، انباشتن SRAM

- یکپارچه سازی سیستم سه بعدی: تراشه، بسته بندی 2.5D/3D، ادغام مبتنی بر interposer

آنها با هم تشکیل می دهند 3D×3D×3D عصر: ترانزیستور، دستگاه و سیستم همگی سه بعدی می شوند.

DTCO: شایستگی اصلی جدید

همانطور که مقیاس بندی به پایان می رسد، بهینه سازی مشترک فناوری طراحی (DTCO) انتقادی می شود.این به معنای طراحی مشترک معماری، ساختار ترانزیستور، مسیریابی فلز و بسته بندی از همان ابتدا است.قویترین شرکتها دیگر فقط رهبران فرآیند نیستند، بلکه یکپارچهکنندههای سطح سیستم هستند.

راندمان سیم کشی، تحویل نیرو، طراحی حرارتی و چگالی پهنای باند اکنون عملکرد واقعی محصول را تعیین می کند.

هوش مصنوعی نیروی محرکه نهایی است

هوش مصنوعی و محاسبات با عملکرد بالا، پهنای باند، کارایی انرژی و چگالی بیسابقهای را طلب میکنند.این الزامات را نمی توان با مقیاس بندی سنتی برآورده کرد.آنها نیاز دارند:

- اتصال محاسباتی حافظه با پهنای باند فوق العاده بالا

- بهره وری انرژی فوق العاده در هر عملیات

- موازی سازی عظیم و یکپارچگی متراکم

هوش مصنوعی کل صنعت را مجبور کرده است که مقیاس بندی خالص را کنار بگذارد و از یکپارچگی ناهمگن سه بعدی کامل استقبال کند.

نتیجه گیری: آینده کوچکتر نیست، بالاتر است

عصر کوچک شدن ترانزیستورها در حال محو شدن است.آینده نیمه هادی ها در مورد کوچکتر کردن دستگاه ها نیست، بلکه در مورد ساخت سیستم ها است متصل تر، متراکم تر و هوشمندتر است.

از Planar تا FinFET تا GAA تا CFET، ترانزیستور تکامل خود را کامل کرده است.نبرد بعدی در آن انجام خواهد شد ادغام سه بعدی، بسته بندی پیشرفته و طراحی در سطح سیستم.اینجاست که دهه آینده رهبری نیمه هادی ها تصمیم گیری می شود.